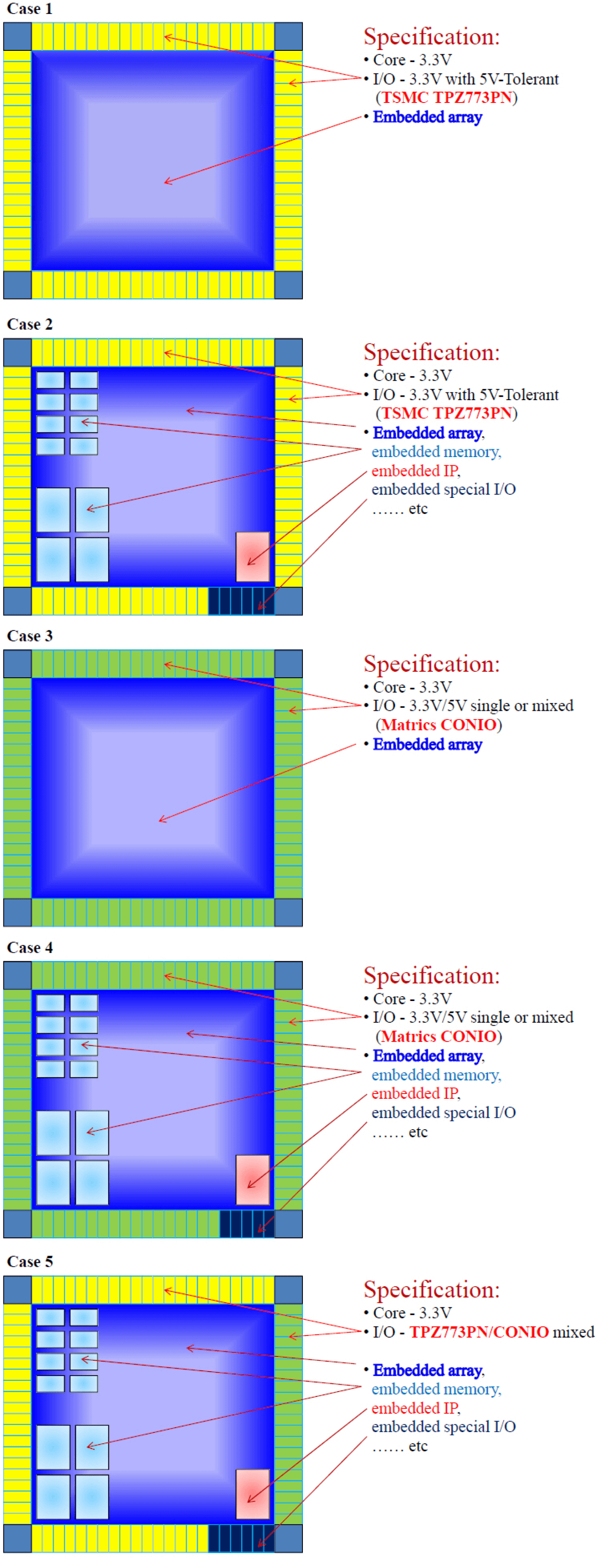

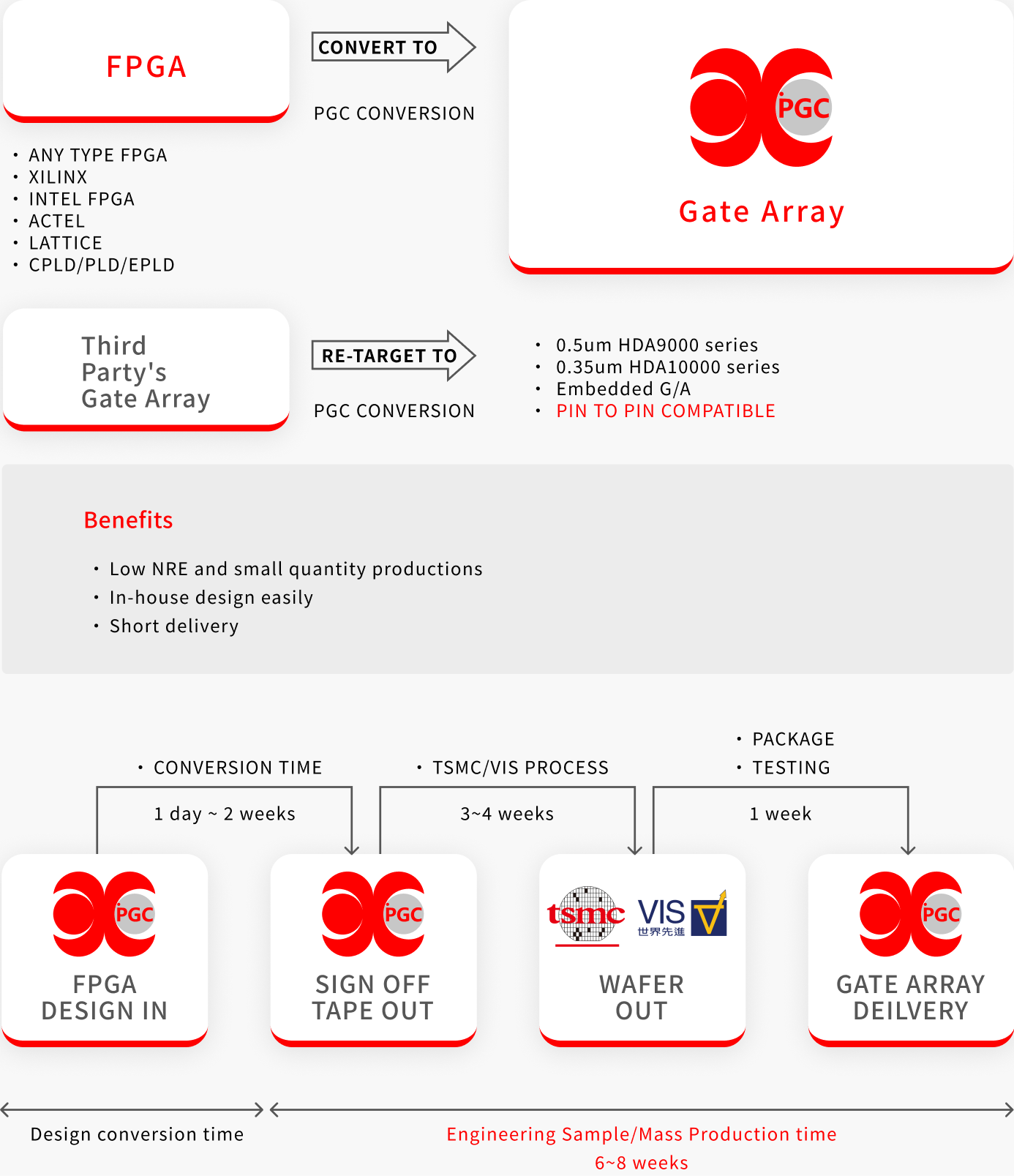

Solution

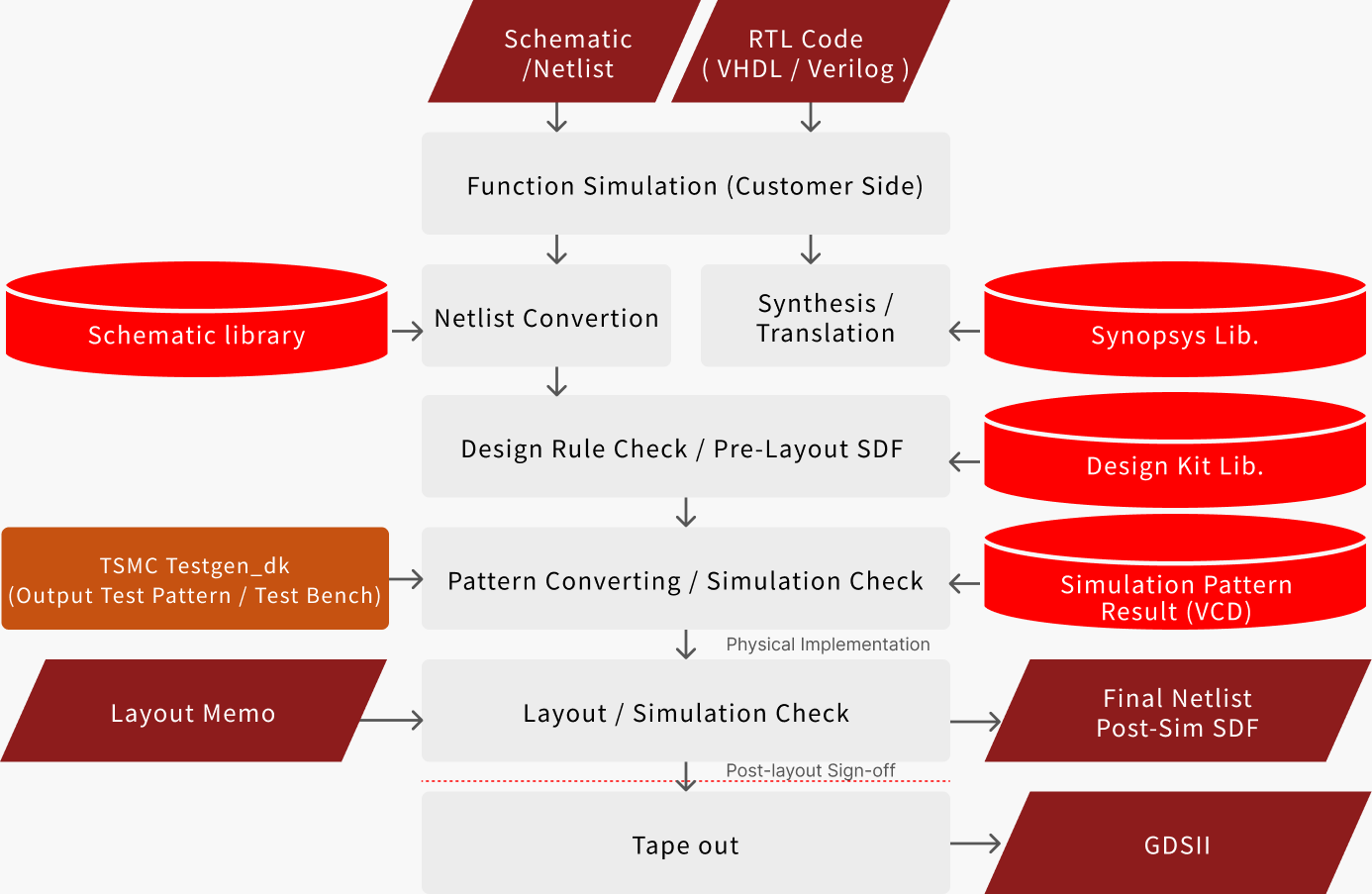

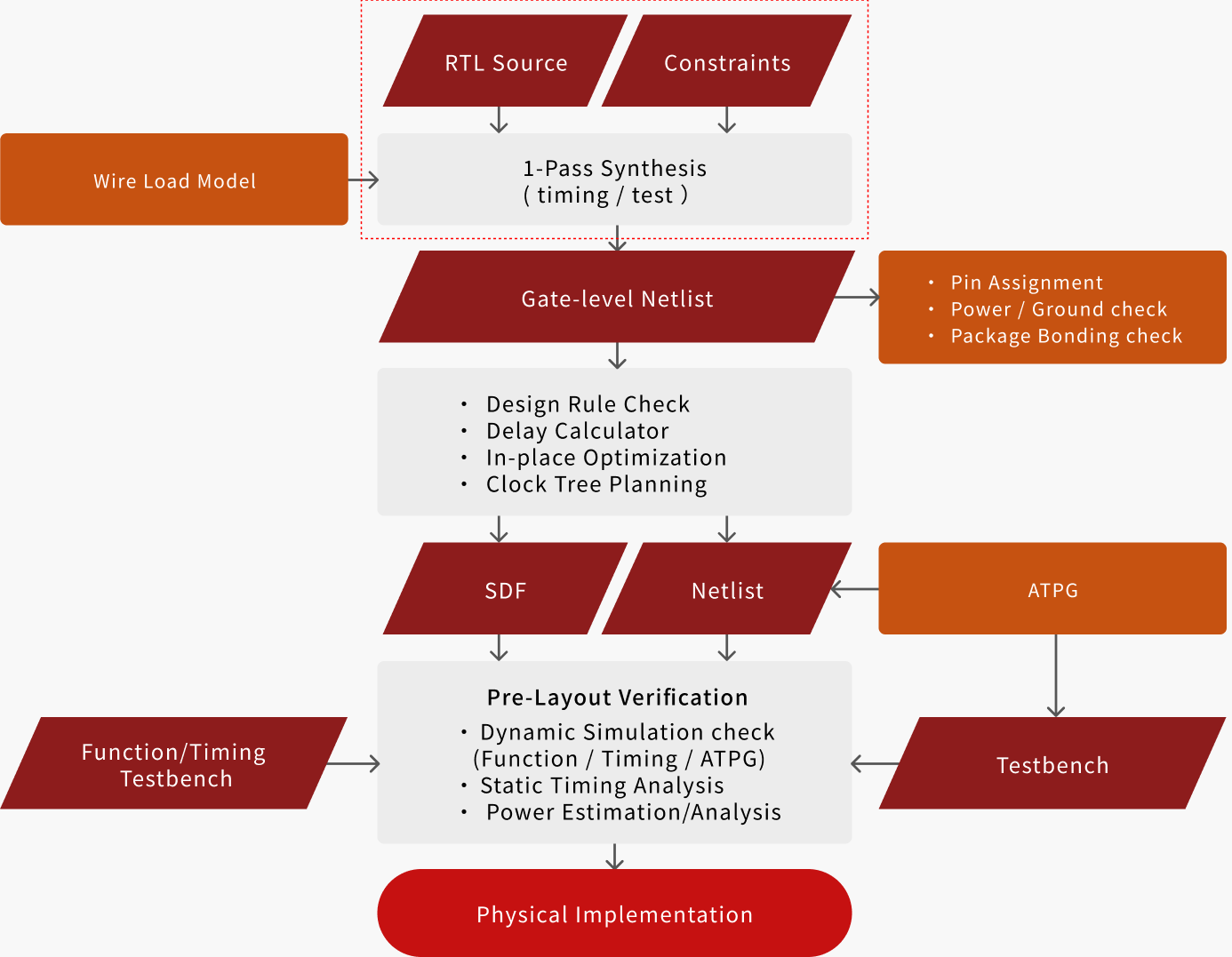

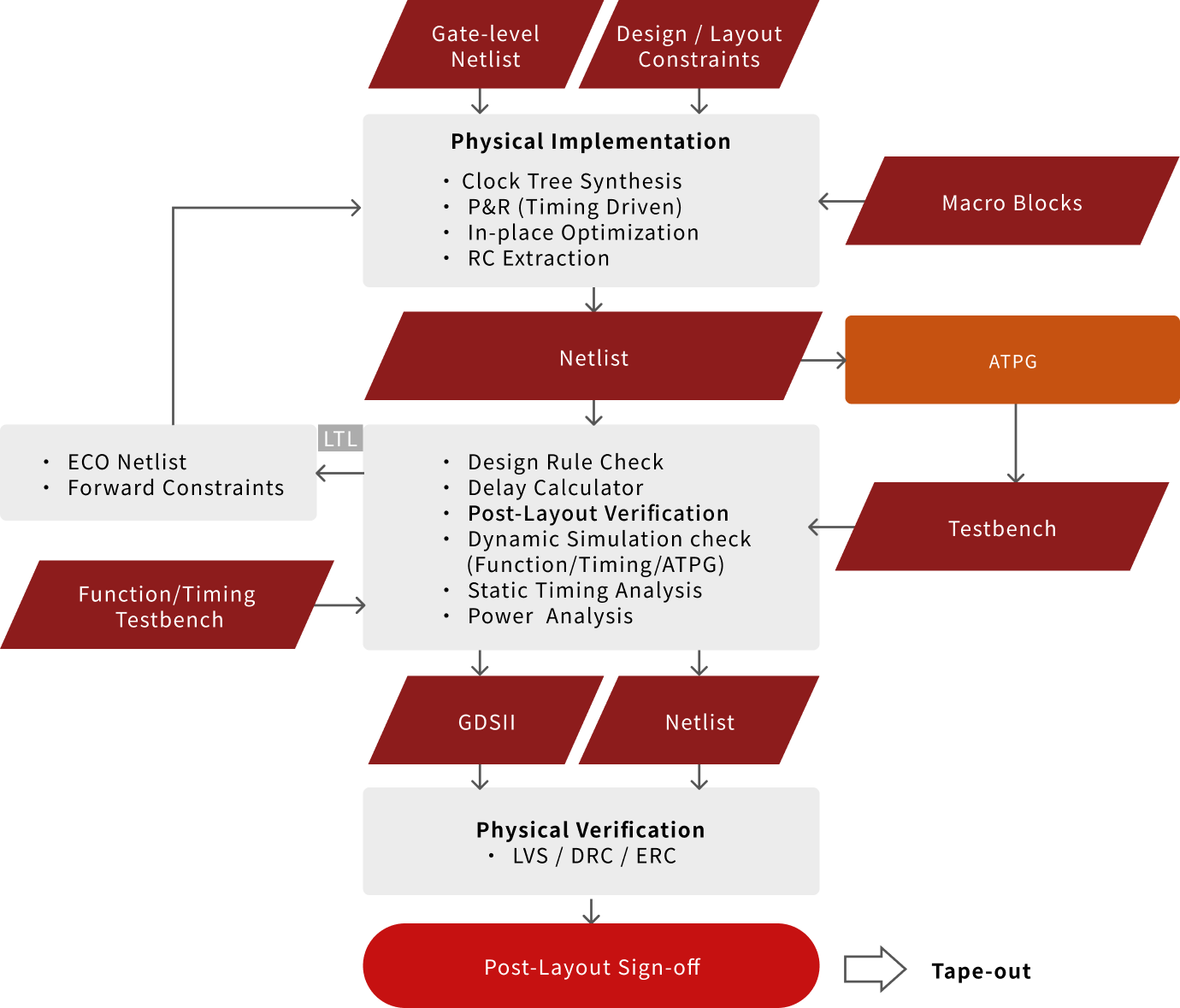

Gate Array Turnkey Service

0.35um GATE ARRAY BODIES @TSMC/VIS FAB

0.35um GATE ARRAY BODIES

@TSMC /VIS FAB

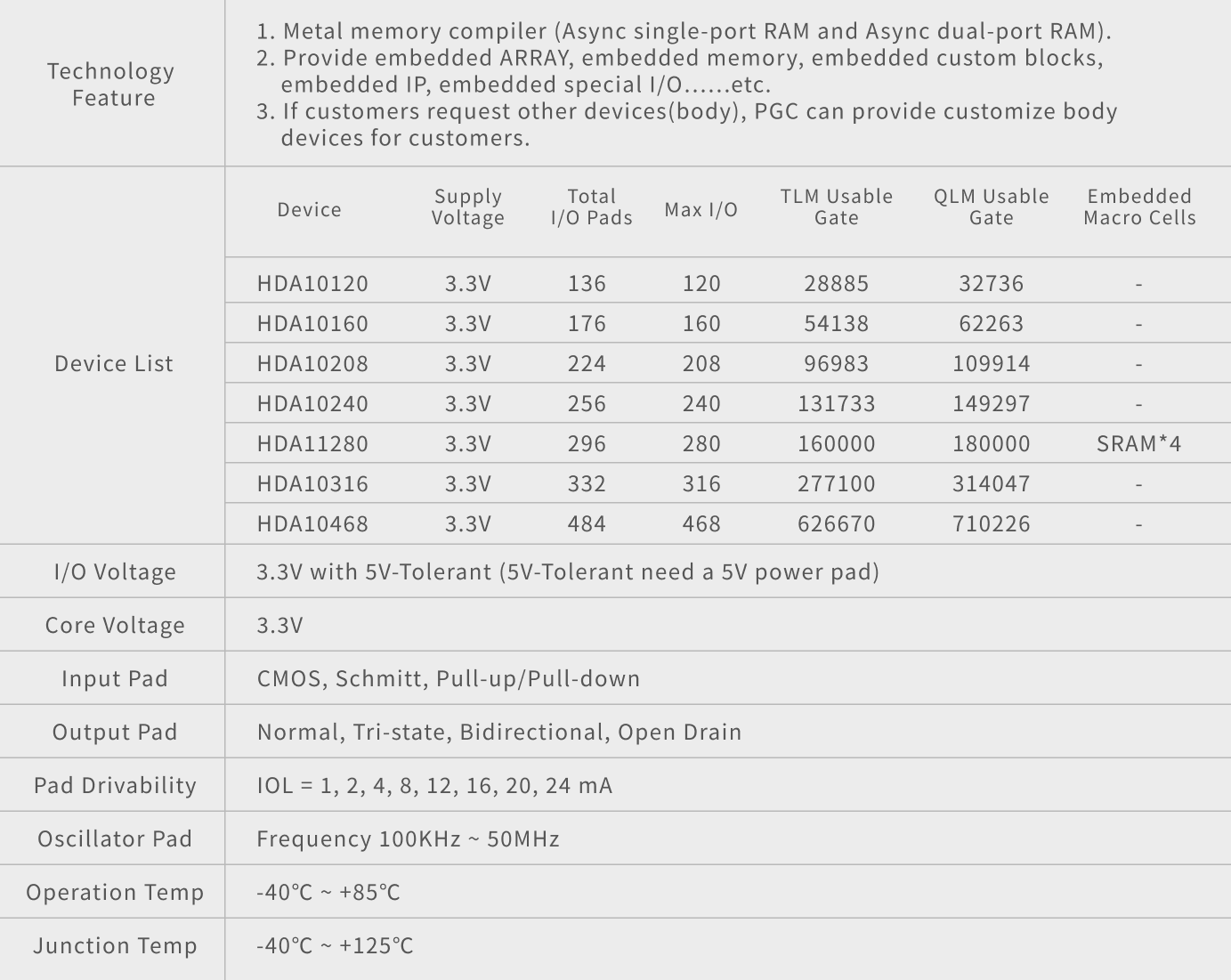

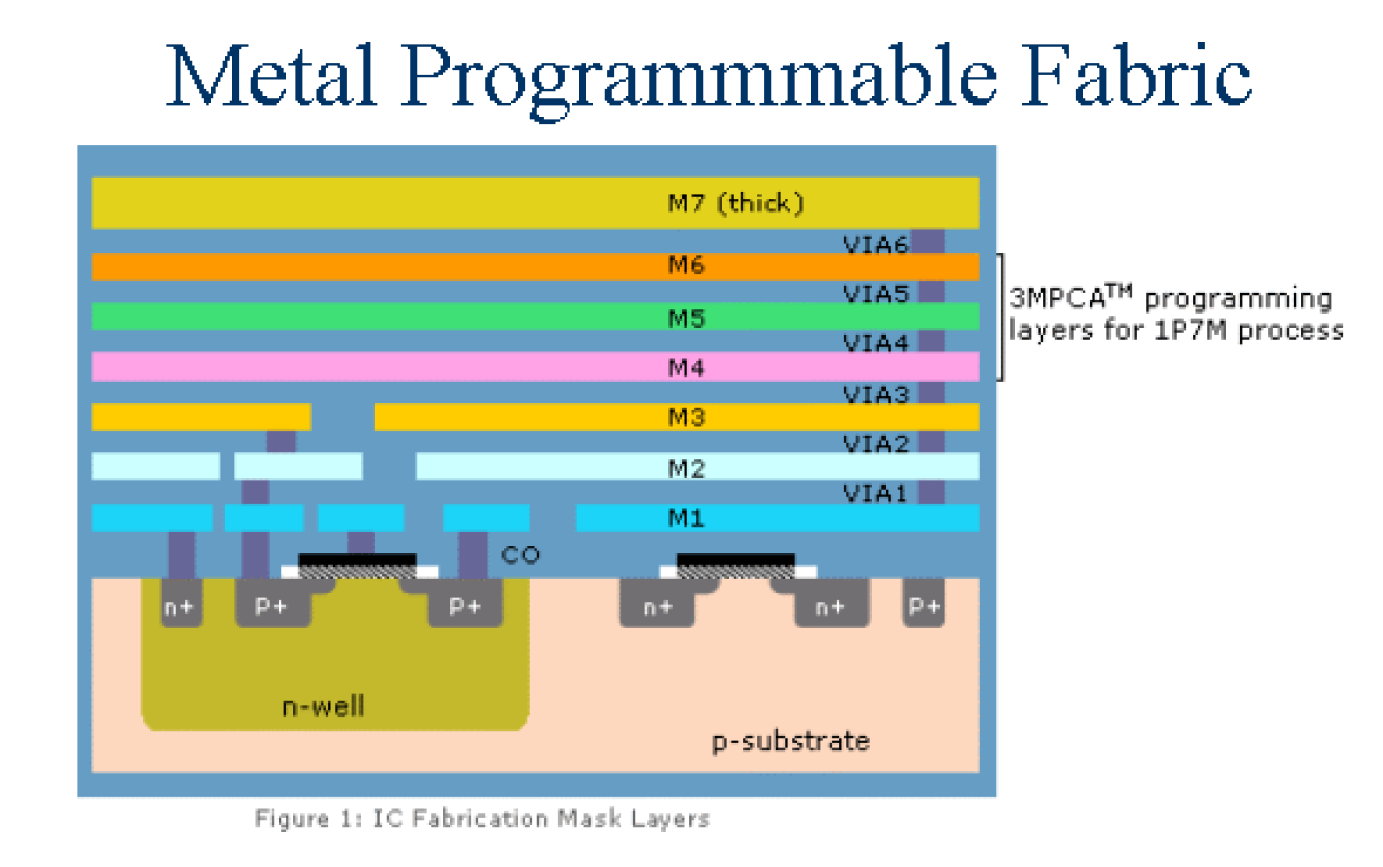

HDA10000 Products 0.35um

5V Tolerant I/O, 3.3V Process, Stagger I/O

8″ wafer TSMC FAB

“Support Special MoQ”

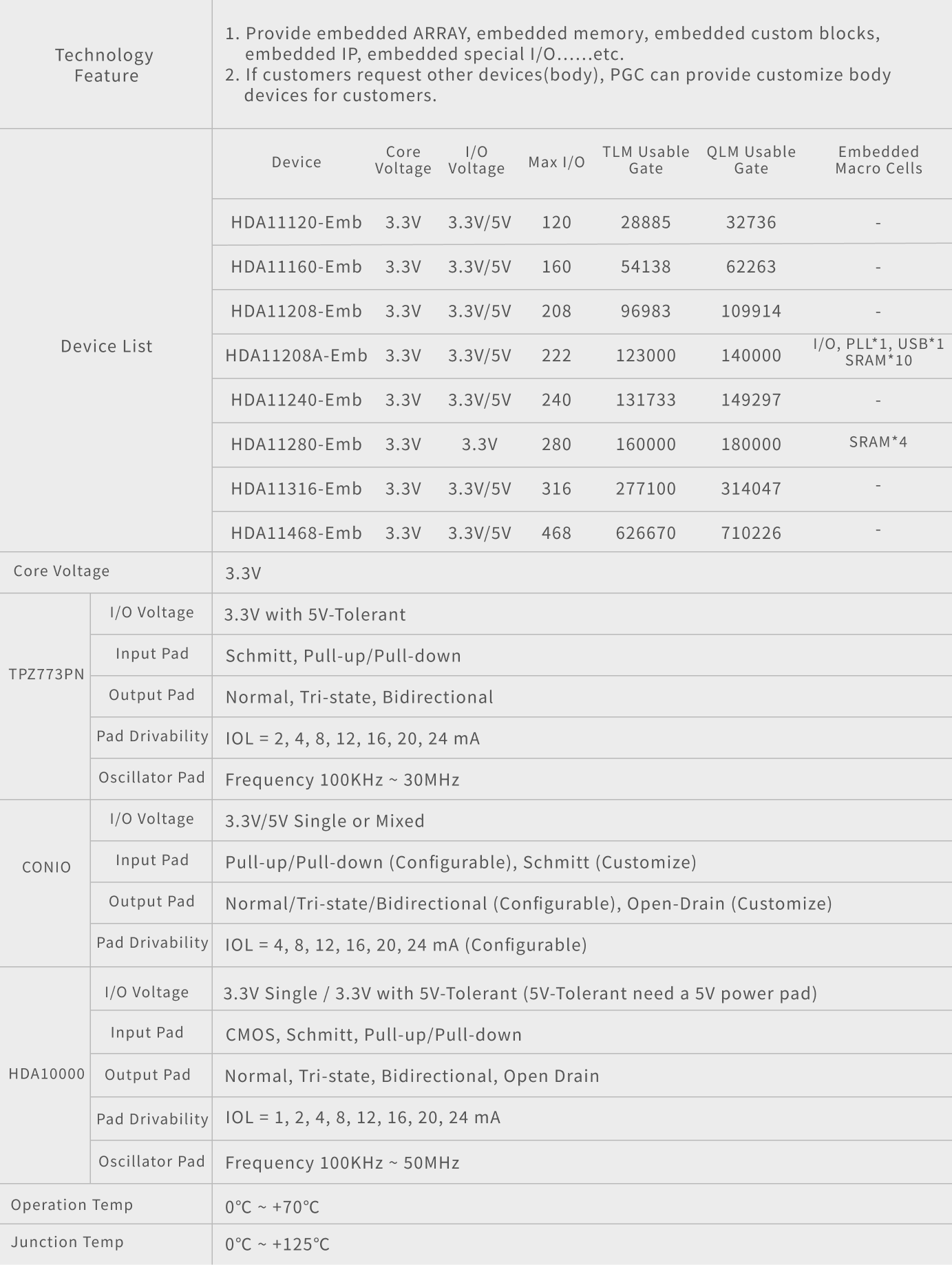

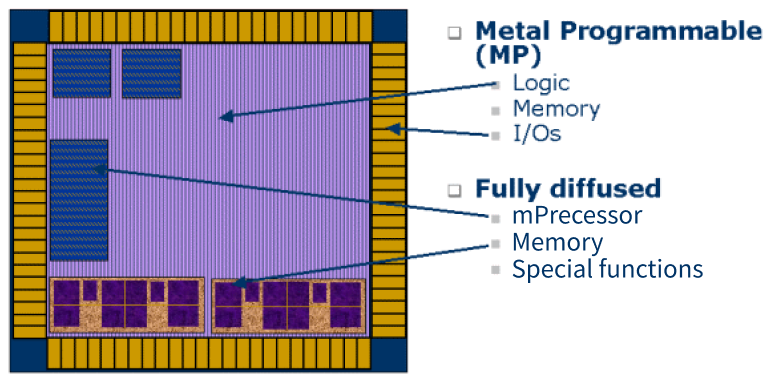

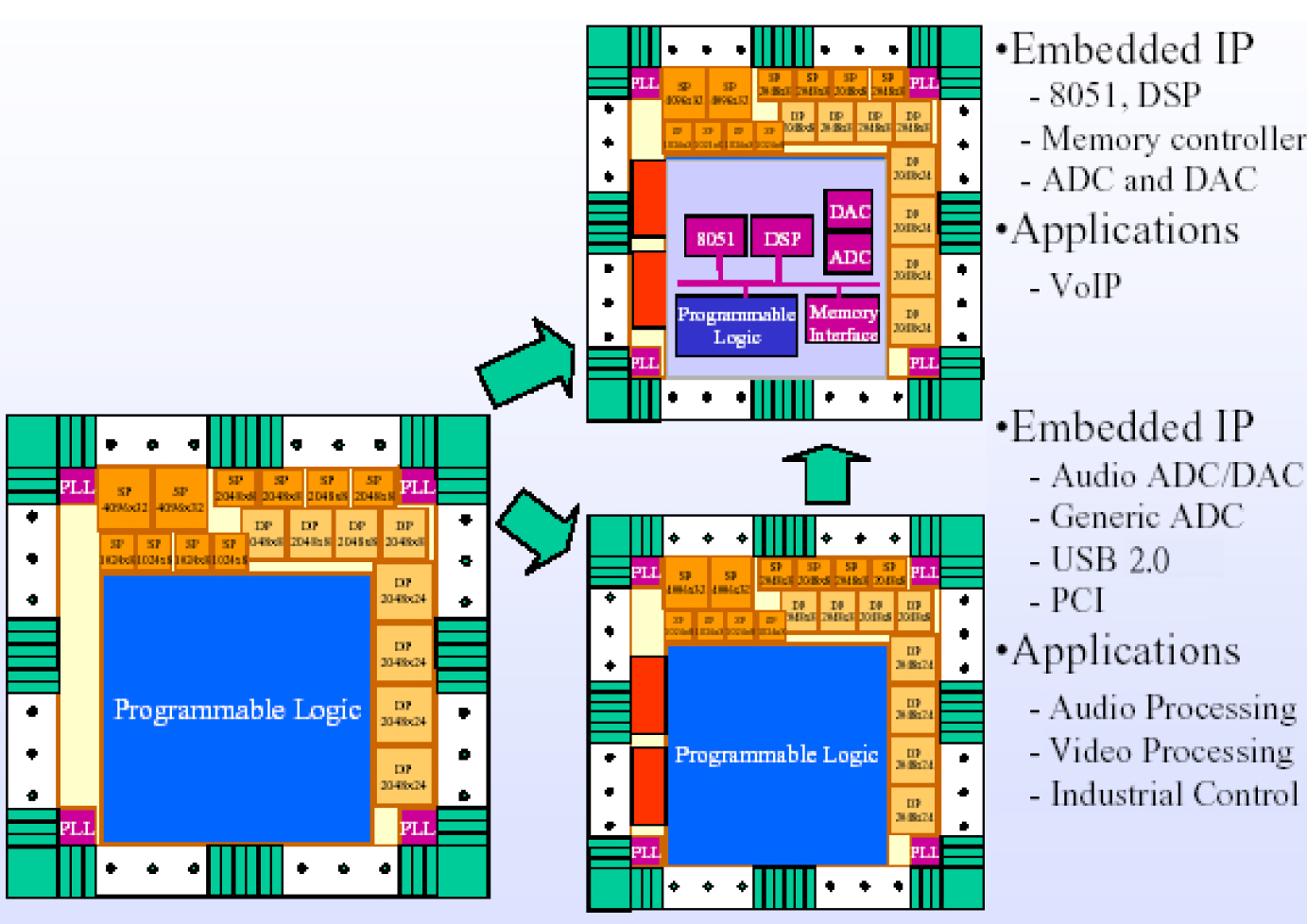

ASPEC 0.35um Embedded Array: HDA11000-Emb Product

ASPEC 0.35um Embedded Array:

HDA11000-Emb Product

8″ wafer TSMC FAB

“Support Special MoQ”

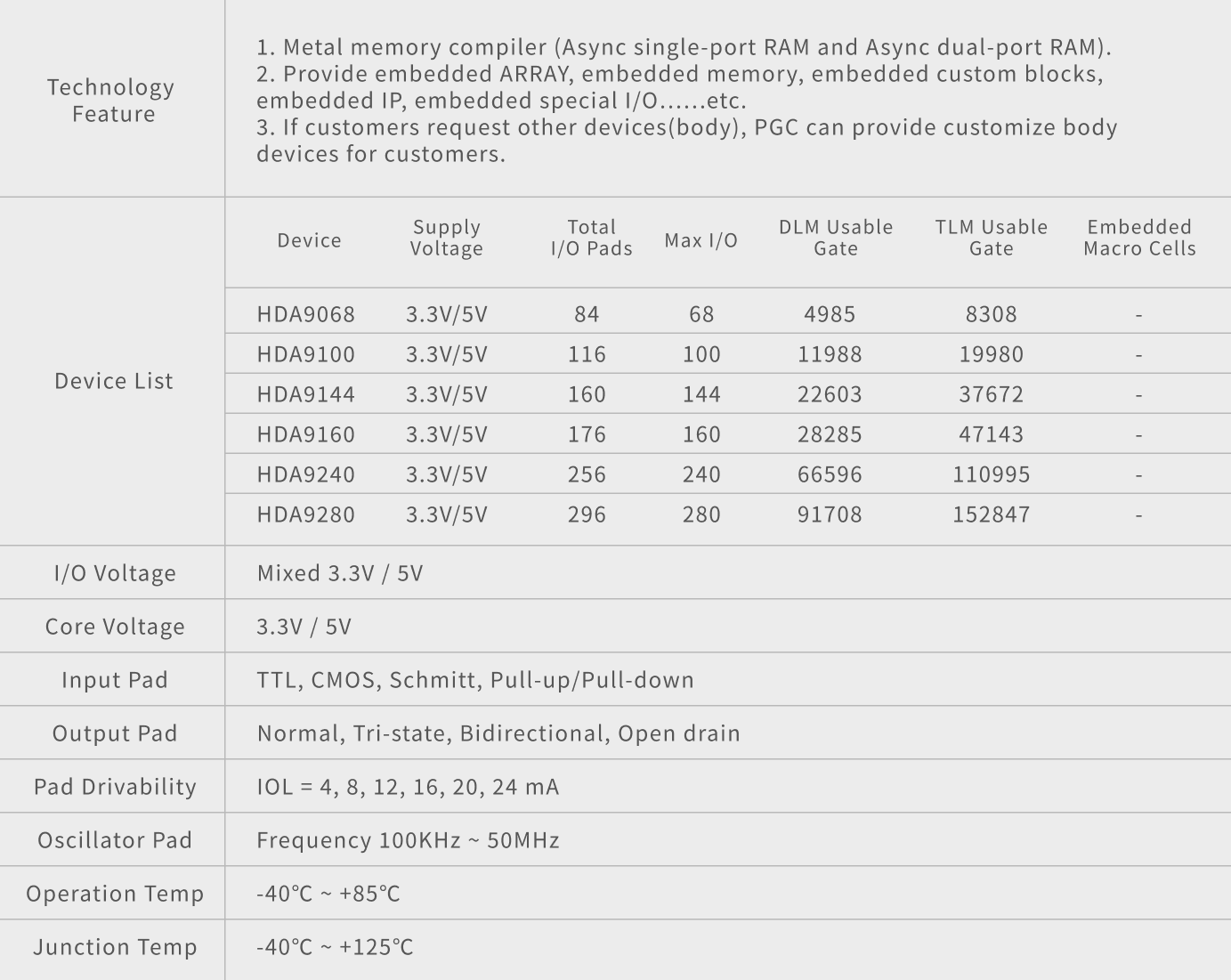

0.5um GATE ARRAY BODIES @TSMC/VIS FAB

0.5um GATE ARRAY BODIES @TSMC/VIS FAB

HDA9000 Products 0.5um

Mixed 3V/5V Power, 5V Process Core: 3V/5V, Stagger I/O

6″/8″ wafer TSMC/VIS FAB

“Support Special MoQ”